RISC-V ne uključuje nikakvu novu tehnologiju.

Ipak, izazvao je ozbiljno međunarodno zanimanje u proteklih desetak godina, otkako su ga 2010. stvorili i osmislili programeri na kalifornijskom sveučilištu Berkley.

RISC-V ("rizik-pet") je arhitektura skupa instrukcija (ISA) utemeljena u sama načela računala smanjenog skupa instrukcija (RISC).

RISC-V je jedinstven, čak i revolucionaran, jer je uobičajeni, besplatni ISA otvorenog koda na koji se može preneti softver, razviti hardver i izgraditi procesori koji ga podržavaju. Od 1981. prethodne generacije RISC arhitekture (I-IV) razvijene su na Kalifornijskom sveučilištu Berkeley.

Neki od najčešćih, ali vlasničkih ISA-ova su x86, ARMv8 i AMD64.

Dok su najčešće korišteni ISA (do sada) vlasnički i zajtevaju licencu i naknade za njihovu upotrebu, RISC-V je dostupan pod licencom otvorenog koda.

Kako bi se dodatno osnažio ISA otvorenog koda, RISC-V Foundation je sazvan 2015. kako bi formirao "zajednicu saradnje softverskih i hardverskih inovatora utemeljenu na RISC-V ISA" i upravljao njegovim razvojem. Fondacija RISC-V stvorena je 2015. godine u partnerstvu s 29 firmi članica kada su izvorni programeri RISC-V-a preneli svoja prava na samu fondaciju. Godine 2020. fondacija je preimenovana u RISC-V International nakon formiranja u Švajcarskoj. Organizacija je narasla na 2000+ članova iz više od 70 zemalja u vremenu od samo nekoliko godina. Članovi RISC-V International uključuju partnere osnivače Google, Qualcomm i Western Digital, da spomenemo samo neke, kao i Arduino, Hitachi i Samsung.

Da bismo razumeli zašto je RISC-V tako pristupačan - čak i izvan svoje najprivlačnije stavke ili prednosti a to je otvorenog kod.

Možemo pobliže pogledati njegove druge važne atribute.

Karakteristike RISC-V

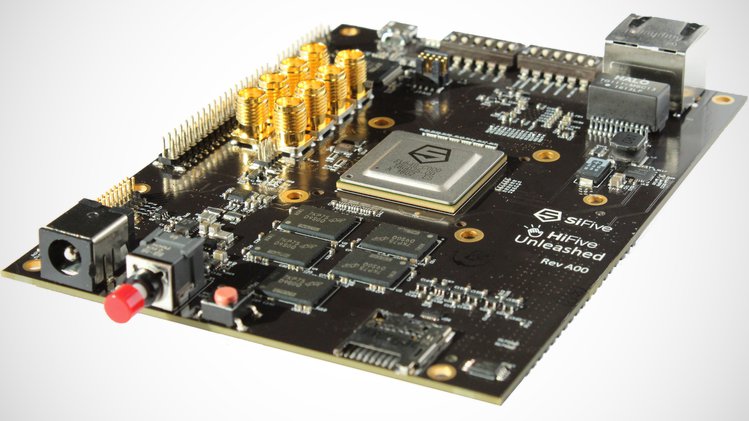

Je dokazani ISA i slijedi utvrđena načela dizajna RISC Ima upustva za jedan ciklus Koristi arhitekturu load-store Ima jednostavan, stabilan dizajn usmeren na softver (mala, fiksna baza s modularnim fiksnim standardnim proširenjima) Modularan je, slojevit i proširiv, dopuštajući softversku i hardversku slobodu u arhitekturi Fleksibilan i skalabilan (tj. pogodan za mikrokontrolere. Od personalnih računara do super računara work station i servera) Ima 32- i 64-bitne varijante i proširenja za podršku instrukcija s pomičnim zarezom Podržavaju ga različiti jezični prevoditelji (npr. GNU Compiler Collection i Linux operativni sistem) Nudi niz hardverske podrške od mikrokontrolera do sistema na modulima, sistema na čipu i poljem programabilnih polja vrata Ubrzava vremenski okvir od dizajna do tržišta kroz saradnju i ponovno korištenje IP-a otvorenog koda.

RISC-V aplikacije kako programeri i proizvođači svih vrsta i veličina nastavljaju implementirati RISC-V, softver, hardver i procesori izgrađeni za i oko ovog ISA otvorenog koda će se razmnožavati.

RISC-V će postati sveprisutan i predviđa se da će otvoriti "put za sledećih 50 godina računarskog dizajna i inovacija."

Razne aplikacije za RISC-V uključuju.

Veštačka inteligencija.

Proširena virtuelna stvarnost.

Automobilski i autoindustrijski domeni na svim poljima.

Korištenje u oblaku.

Računarski uređaji i upravljači.

Procesori opšte namene.

Internet stvari.

Mašinsko učenje.

Mrežni hub i ostala infrastruktura mreža.

Virtualna stvarnost Dokazana priroda otvorenog koda RISC-V je ključna jer omogućuje manjim programerima i proizvođačima da dizajniraju i grade hardver bez troškova licenciranja vlasničkih ISA-ova i plaćanja datih licenci.

Kao rezultat toga, firme svih veličina mogu inovirati i stvarati, stavljajući najbolje proizvode na tržište za napredak industrije i dobrobit potrošača u celini.

Izgovara se kao "rizik pet", RISC-V je ISA koji se formira na principima računara sa smanjenim skupom instrukcija (RISC).

Arhitektura skupa instrukcija (ISA) deo je apstraktnog modela računara koji daje definiciju kako CPU kontroliše softver.

ISA deluje kao komandni most između hardvera i softvera, određujući šta procesor može raditi kao i kako to radi.

riscv.org

RISC-V allows smaller device manufacturers to build hardware without paying royalties, and encourage innovation and competition.

www.ics.com

The revolution is happening, but what is RISC-V? This blog post clarifies things for you, as Codasip cares about it, and you should too!

codasip.com

RISC-V is an instruction set architecture for processors that offers innovative operational mechanisms. Learn about its background and the advantages it brings.

www.techrepublic.com

What is RISC-V RISC-V is an open standard instruction set architecture (ISA) based on established

www.seeedstudio.com

A brief history of the open ISA.

semiengineering.com

developer.nvidia.com

developer.nvidia.com